MCA-02/MSc IT-02/PGDCA-02

# **UTTARAKHAND OPEN UNIVERSITY**

## **Master of Computer Application**

## **DIGITAL LOGIC**

KRISHNA KANTA HANDIQUE STATE OPEN UNIVERSITY Housefed Complex, Dispur, Guwahati - 781 006

## **Subject Expert**

#### Prof. Anjana Kakati Mahanta,

Deptt. of Computer Science, Gauhati University

#### Prof. Jatindra Kr. Deka,

Deptt. of Computer Science and Engineering, Indian Institute of Technology, Guwahati

#### Prof. Diganta Goswami,

Deptt. of Computer Science and Engineering, Indian Institute of Technology, Guwahati

#### **Course Coordinator**

Tapashi Kashyap Das, Assistant Professor, Computer Science, KKHSOU

Arabinda Saikia, Assistant Professor, Computer Science, KKHSOU

### SLM Preparation Team

#### UNITS CONTRIBUTORS

- 1 & 6 Prof. Jyotiprokash Goswami, Deptt. of Computer Applications, Assam Engineering College, Guwahati, Assam

- **4 & 5 Chakradhar Das,** Lecturer (Selection Grade), Deptt. of Eletrical Engineering, Bongaigaon Polytechniq, Assam

- 2 & 3 Sangeeta Kakoty, Lecturer Deptt. of Computer Science, Jagiroad College, Assam

#### July - 2014

© Krishna Kanta Handiqui State Open University.

No part of this publication which is material protected by this copyright notice may be produced or transmitted or utilized or stored in any form or by any means now known or hereinafter invented, electronic, digital or mechanical, including photocopying, scanning, recording or by any information storage or retrieval system, without prior written permission from the KKHSOU.

The university acknowledges with thanks the financial support provided by the **Distance Education Council**, **New Delhi**, for the preparation of this study material.

Printed and published by Registrar on behalf of the Krishna Kanta Handiqui State Open University.

Housefed Complex, Dispur, Guwahati- 781006; Web: www.kkhsou.org

#### Academic and Administrative Arrangement

**Prof. Subhash Dhuliya** Vice-Chancellor Uttarakhand Open University Shri. L.S. Rawat Registrar Uttarakhand Open University Smt. Leela Rawat Incharge, Study Material Uttarakhand Open University

#### Production: July 2014

All right reserved No part of this book may be reproduced in any form by mimerograph or any other means, without permission in writing form the Krishna Kanta Handiqui State Open University, Guwahati.

Uttarakahnd open University acknowledges with thanks the support by KKHSOU, Guwahati for Sharing the material.

#### Printed by : Uttarayan Prakashan, Haldwani

## **COURSE INTRODUCTION**

This is a course on **Digital Logic**. Digital logic has facinated many people over the years. Everything in the digital world is based on the binary number system. Numerically, this involves only two symbols: 0 and 1. Digital Logic is a method by which electrical circuits are provided with a limited ability to make decisions. The most common use of digital logic today is in the control and arithmetic functions of digital computers, without which modern life would grind to a halt.

The course consists of six units :

The *first* unit discusses various number systems like decimal, binary, octal, hexadecimal and their conversion from one form to another. The unit also includes the methods of addition and sub-traction of binary numbers, complements and fixed/floating point representations. Concept of BCD, ASCII, EBCDIC, Gray code etc are discussed at the end.

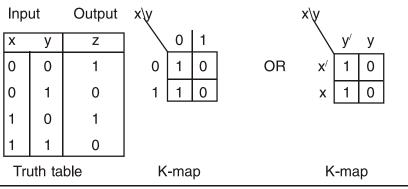

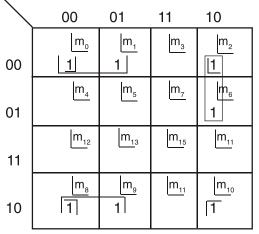

The *second* unit is on Boolean Algebra. The unit discusses various concept assotiated with Boolean Algebra like Boolean operators, Boolean expression, representation of Boolean expression in Canonical form, Karnaugh Map, Don't care condition etc.

The *third unit* discusses various logic gates, their conversion, truth tables, and the most important De-Morgan's theorem.

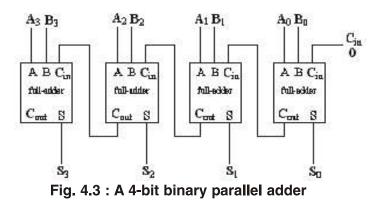

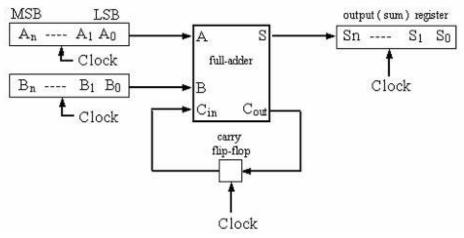

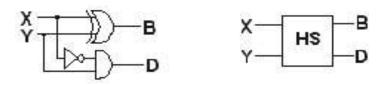

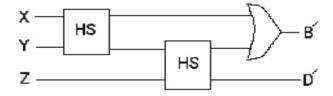

The *fourth unit* focuses on combinational circuits. This unit gives us the concept various adders and subtractors, multiplexers, demultiplexers, encoders, decoders etc. with their applications.

The *fifth unit* deals with sequential circuits which includes the concept of flip-flops, counters, registers.

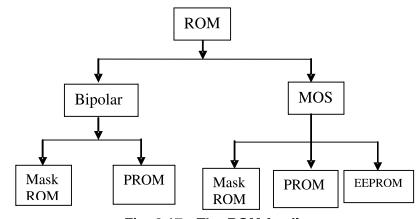

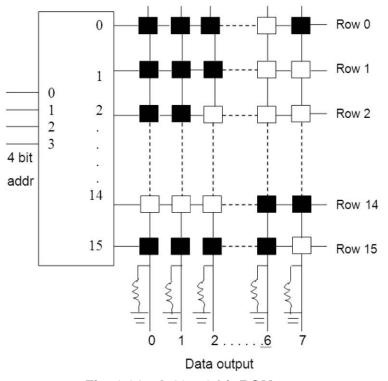

The *sixth* unit is the last unit of this course which is on memory organization. This unit gives us the concept of RAM and its types, 2D and 3D organization of RAM, ROM, types of ROM, organization of simple ROM cell etc.

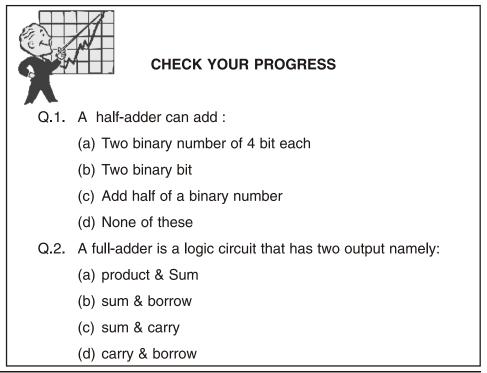

Each unit of this course includes some along-side boxes to help you know some of the difficult, unseen terms. Some "EXERCISES" have been included to help you apply your own thoughts. You may find some boxes marked with: "LET US KNOW". These boxes will provide you with some additional interesting and relevant information. Again, you will get "CHECK YOUR PROGRESS" questions. These have been designed to self-check your progress of study. It will be helpful for you if you solve the problems put in these boxes immediately after you go through the sections of the units and then match your answers with "ANSWERS TO CHECK YOUR PROGRESS" given at the end of each unit.

## **MASTER OF COMPUTER APPLICATIONS**

## **Digital Logic**

### DETAILED SYLLABUS

|          |                                                                                                                                                                                                                                                                                                                                         | Marks                                                                                                                                      | Page No.                                     |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| UNIT 1 : | Number Systems<br>Decimal, Binary, Hexadecimal and Octal. It's (<br>Octal and vice versa. Addition/ Subtraction<br>(r-1)'s complement. Fixed Point representation<br>ASCII, EBCDIC, Gray code.                                                                                                                                          | on Binary Numbers, Complem                                                                                                                 | ent: r's and                                 |

| UNIT 2 : | <b>Boolean Algebra</b><br>Boolean operators, Rules (postulates and bac<br>complement of Boolean expression, represe<br>form, Boolean expression and their simplificat<br>Don't care condition.                                                                                                                                          | ntation of Boolean expression in                                                                                                           | n Canonical                                  |

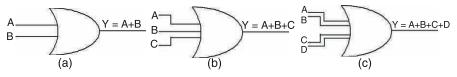

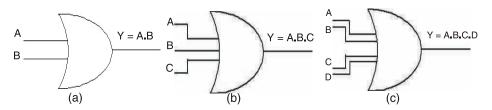

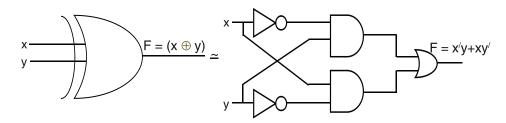

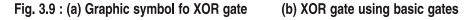

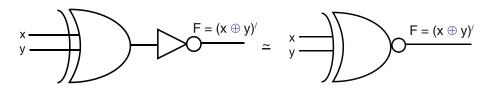

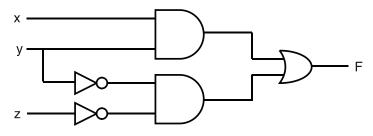

| UNIT 3 : | Logic Gates<br>Logic Gates(OR, AND, NOT, NAND, NOR,<br>theorem, Conversion of the logic gates.                                                                                                                                                                                                                                          | <b>15</b><br>, XOR, XNOR), Truth Tables, D                                                                                                 | <b>68-87</b><br>De-Morgan's                  |

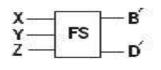

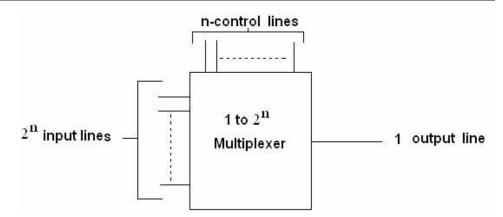

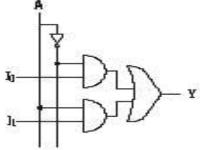

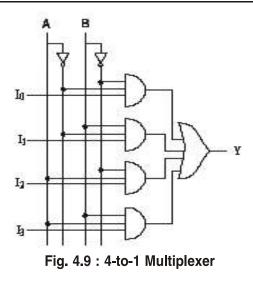

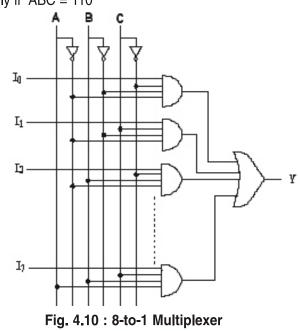

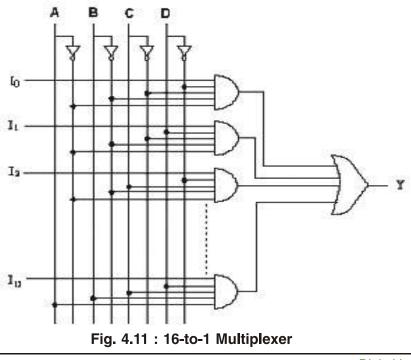

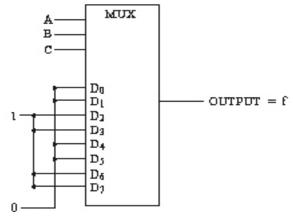

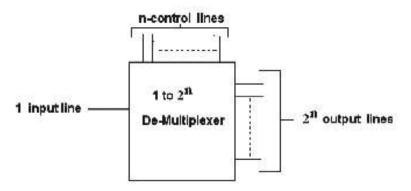

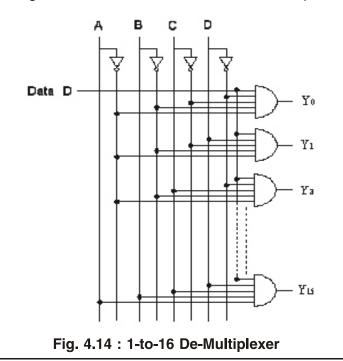

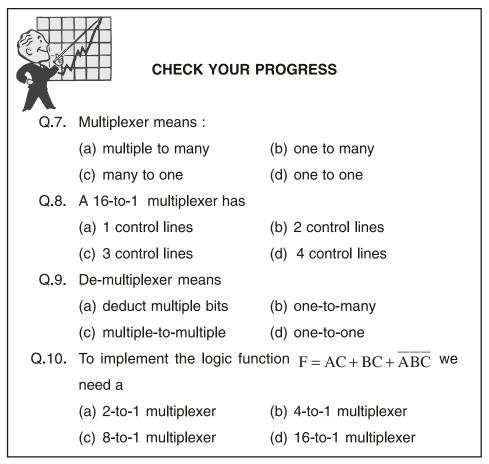

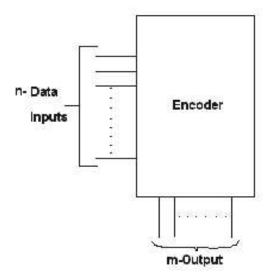

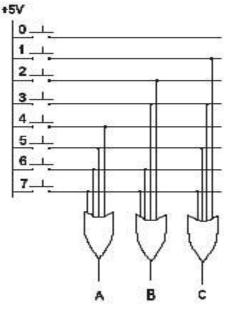

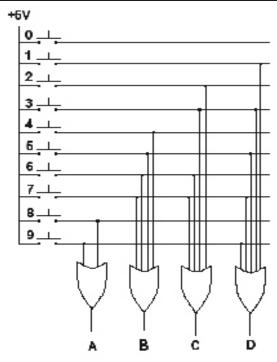

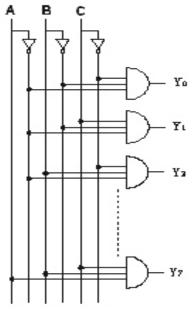

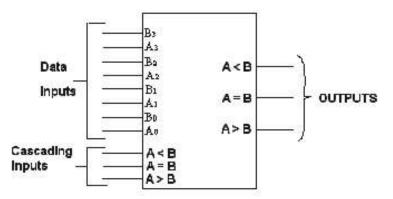

| UNIT 4 : | <b>Combinational Circuits</b><br>Introduction to Combinational Circuits; Half-a<br>Binary Parallel Adder, Serial Adder; Half-sub-<br>Input Multiplexer, 4-Input-Multiplexer, 8-to-1<br>Applications; Demultiplexer: Parallel-to-Se<br>Demultiplexer; Encoder: Octal-to-Binary Encoder<br>Basic Binary Decoder, 3-line-to-8-Line Decoder | tractor, Full-subtractor; Multiplex<br>Multiplexer, 16-to-1 Multiplexer,<br>erial Converter, Data Distribu<br>coder, Decimal-to-BCD Encode | ker: Basic 2-<br>Multiplexer<br>tors, 1-to-4 |

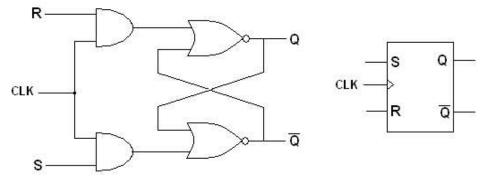

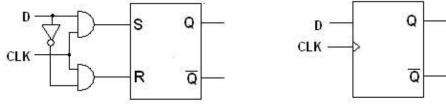

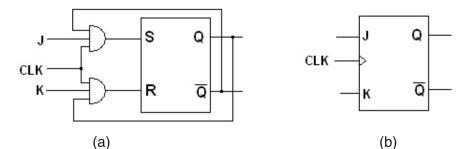

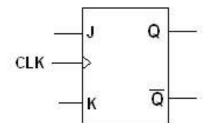

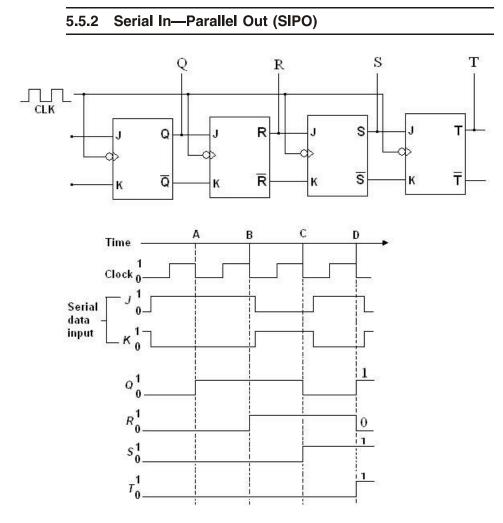

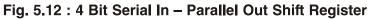

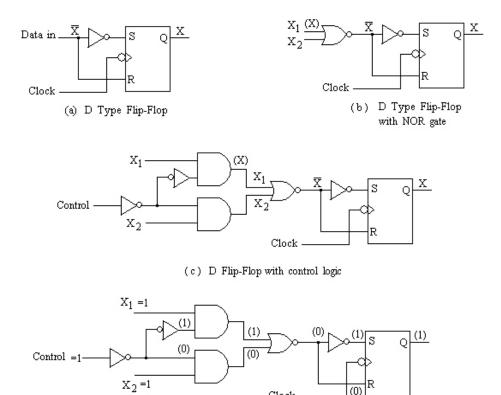

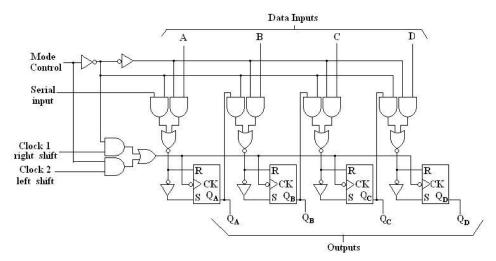

| UNIT 5 : | Sequential Circuits<br>Sequential Circuits; Flip-Flops: RS, D, JK, M<br>Registers and its types, Shift Registers: Seria<br>Shift-Right Register, Serial-in-Parallel-out S<br>Registers, Parallel-in-Parallel-out Register, A                                                                                                            | al in-Serial out Registers, Shift-L<br>Shift Registers, Parallel-in-Ser                                                                    | eft Register,                                |

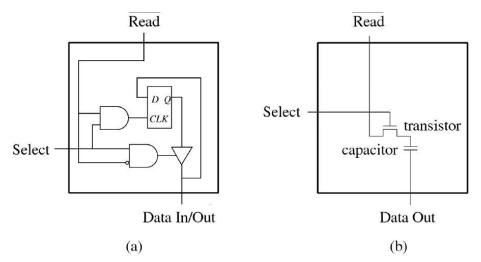

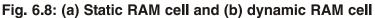

| UNIT 6 : | Memory Organization<br>Random Access Memory : Types of RAM; St                                                                                                                                                                                                                                                                          | 15<br>atic RAM : Static RAM cell and i                                                                                                     | 136-160<br>its structure;                    |

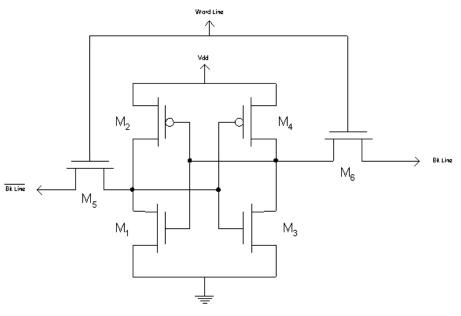

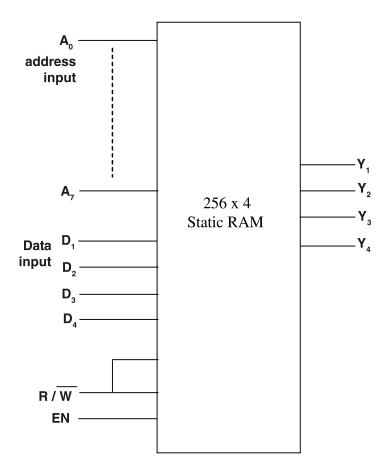

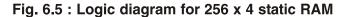

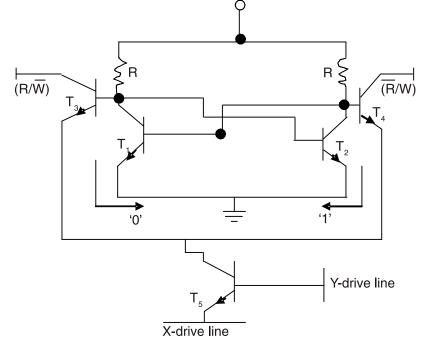

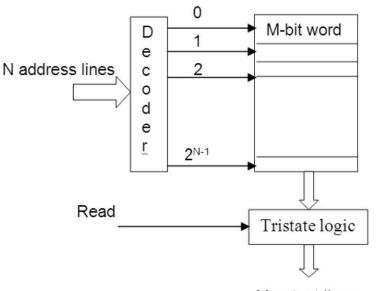

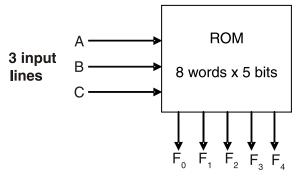

Random Access Memory : Types of RAM; Static RAM : Static RAM cell and its structure; DRAM : basic structure of DRAM; Organization of RAM : 2D organization, 3D organization; ROM : Types of ROM, organization of simple ROM cell.

## UNIT 1 : NUMBER SYSTEMS

## **UNIT STRUCTURE**

- 1.1 Learning Objectives

- 1.2 Introduction

- 1.3 Number System

- 1.3.1 Decimal Number System

- 1.3.2 Binary Number System

- 1.3.3 Octal Number System

- 1.3.4 Hexadecimal Number System

- 1.4 Number System Conversion

- 1.4.1 Binary to Decimal Conversion

- 1.4.2 Decimal to Binary Conversion

- 1.4.3 Octal to Decimal conversion

- 1.4.4 Decimal to Octal Conversion

- 1.4.5 Hexadecimal to decimal Conversion

- 1.4.6 Decimal to Hexadecimal Conversion

- 1.5 Complement of Numbers

- 1.5.1 (r-1)'s Complement

- 1.5.2 r's complement

- 1.6 Data Representation

- 1.6.1 Fixed Point Representaion

- 1.6.2 Floating Point Representation

- 1.7 Binary Arithmatic

- 1.7.1 Addition

- 1.7.2 Subtraction

- 1.7.3 Multiplication

- 1.7.4 Division

- 1.8 Computer Codes

- 1.8.1 BCD

- 1.8.2 ASCII

- 1.8.3 EBCDIC

- 1.8.4 Gray Code

- 1.9 Let Us Sum Up

- 1.10 Answers to Check Your Progress

- 1.11 Further Readings

- 1.12 Model Questions

#### 1.1 LEARNING OBJECTIVES

After going through this unit, you will be able to :

- define and describe number system

- identify how data is represented in computers

- convert a number from one number system to anotehr

- describe how computers perform binary arithmatic

- describe the different types computer codes

#### **1.2 INTRODUCTION**

Number system is a fundamental concept used in micro computer system. They are of different types and can represent by some digit symbols. The knowledge of binary, octal and hexadecimal number system is essential to understand the operation of a computer. This unit deals with all this system. In this unit we will discuss about all the representation of this number system and their conversion from one number system to its equivalent other number system. The arithmetic operations of all the system is very much important to know how a system can operate our data inside. This is also discussed in this unit. In addition you we will get the internal data representation method which is called computer codes. Different computer codes like BCD code, ASCII, EBCDIC etc are introduced here in this unit.

#### **1.3 NUMBER SYSTEM**

We are familier with the decimal number system which is used in our day-to-day work. Ten digits are used to four decimal number. To represent these decimal digits, ten separate symbols 0, 1, 2, 3, 4, 5, 6, 7, 8 and 9 are used. But a digital computer stores, understands and manipulates information composed of only zeros and ones. So, each decimal digits, letters, symbols etc. written by the programmer (an user) are converted to binary codes in the form of 0's and 1's within the computer. The number system is divided into different categories according to the base (or radix) of the system as binary, octal and hexadecimal. If a number system of base r is a system, then the system have r distinct symbols for r digits. The knowledge of the number system is essential to understand the operation of a computer.

#### 1.3.1 Decimal Number System

Decimal no. system have ten digits represented by 0, 1, 2, 3, 4, 5, 6, 7, 8 and 9. So, the base or radix of such system is 10.

In this system the successive position to the left of the decimal point represent units, tens, hundreds, thousands etc. For example, if we consider a dicimal number 1257, then the digit representations are :

| 1         | 2        | 5        | 7        |

|-----------|----------|----------|----------|

| ↓         | Ļ        | ↓        | Ļ        |

| thousands | hundreds | tens     | units    |

| positions | position | position | position |

The weight of each digit of a number depends on its relative position within the number.

#### Example 1.1 :

The weight of each digit of the decimal no. 6472  $6472 = 6000 + 400 + 70 + 2 = 6 \times 10^3 + 4 \times 10^2 + 7 \times 10^1 + 2 \times 10^0$ The weight of digits from right hand side are : Weight of 1st digit =  $2 \times 10^0$ Weight of 2nd digit =  $7 \times 10^1$ Weight of 3rd digit =  $4 \times 10^2$ Weight of 4th digit =  $6 \times 10^3$ The above expressions can be written in general forms as the

weight of n<sup>th</sup> digit of the number from the right hand side :

*Decimal Number System* uses 10 digits from 0 to 9 to represents its system.

A *Binary Number System* uses only digit 0 and 1  $= n^{th} digit \times 10^{n-1}$

$= n^{th} digit \times (base)^{n-1}$

The no. system in which the weight of each digit depends on its relative position within the number is called positional number system. The above form of general expression is true only for positional number system.

#### 1.3.2 Binary Number System

Only two digits 0 and 1 are used to represent the binary number system. So the base or radix is two (2). The digits 0 and 1 are called bits (Binary Digits). In this number system the value of the digit will be two times greater than its predecessor. Thus the value of the places are :

$\leftarrow \leftarrow 32 \leftarrow 16 \leftarrow 8 \leftarrow 4 \leftarrow 2 \leftarrow 1$

The weight of each binary bit depends on its relative position within the number. It is explained by the following example--

#### Example 1.2 :

The weight of bits of the binary number 10110 is :

$= 1 \times 2^4 + 0 \times 2^3 + 1 \times 2^2 + 1 \times 2^1 + 0 \times 2^0$

= 16 + 0 + 4 + 2 + 0 = 22 (decimal number)

The weight of each bit of a binary no. depends on its relative pointer within the no. and explained from right hand side as :

Weight of 1st bit = 1st bit X  $2^{\circ}$

Weight of 2nd bit = 2nd bit X  $2^1$

.....

.....

and so on.

The weight of the  $n^{\mbox{\tiny th}}$  bit of the number from right hand side

$= n^{th} bit \times 2^{n-1}$

$= n^{th} bit \times (Base)^{n-1}$

It is seen that this rule for a binary number is same as that for a decimal number system. The above rule holds good for any other

positioned number system. The weight of a digit in any positioned number system depends on its relative positon within the number and the base of the number system.

Table 1.1 shows the binary equivalent numbers for decimal digits.

| Decimal Number | Equivalent Binary Number |

|----------------|--------------------------|

| 0              | 0                        |

| 1              | 1                        |

| 2              | 10                       |

| 3              | 11                       |

| 4              | 100                      |

| 5              | 101                      |

| 6              | 110                      |

| 7              | 111                      |

| 8              | 1000                     |

| 9              | 1001                     |

Table 1.1 : Binary equivalent of decimal numbers

**Binary Fractions :** A binary fractions can be represented by a series of 1s and 0s to the right of a binary point. The weight of digit positions to the right of the binary point are given by 2<sup>-1</sup>, 2<sup>-2</sup>, 2<sup>-3</sup> and so on.

**Example 1.3 :** Show the representation of binary fraction 0.1101.

Solution : The binary representation of 0.1101 is :

$0.1101 = 1 \times 2^{-1} + 1 \times 2^{-2} + 0 \times 2^{-3} + 1 \times 2^{-4}$  $= 1 \times 0.5 + 1 \times 0.25 + 0 \times 0.125 + 1 \times 0.0625$ = 0.8125

So,  $(0.1101)_2 = (0.8125)_{10}$

#### 1.3.3 Octal Number System

A commonly used positional number system is the Octal Number System. This system has eight (8) digit representation as 0,1,2,3,4,5,6 and 7. The base or radix of this system is 8. The values increase from left to right as 1,8,64,512, 4096 etc. The decimal

Octal Number System uses 8 digits from 0 to 7.

value 8 is represented in octal as 10,9 as 11,10 as 12 and so on. As  $8=2^3$ , an octal number is represented by a group of three binary bits. For example 3 is represented as 011, 4 as 100 etc.

Table 1.2 The octal number and their binary representations.

| Decimal Number | Octal Number | Binary Coded Octal No. |

|----------------|--------------|------------------------|

| 0              | 0            | 000                    |

| 1              | 1            | 001                    |

|                |              |                        |

|                |              |                        |

| 7              | 7            | 111                    |

| 8              | 10           | 100 000                |

| 15             | 17           | 001 111                |

## 1.3.4 Hexadecimal Number System

The hexadecimal number system is now extensively used in computer industry. Its base (or radix) is 16, ie. 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, E, F. The hexadecimal numbers are used to represent binary numbers because of case of conversion and compactness.

As  $16 = 2^4$ , hexadecimal number is represented by a group of four binary bits. For example, 5 is represented by 0101. Table 2.3 shows the binary equivalent of a decimal number and its hexadecimal representation.

| Table 1.3 : Hexadecima | I number and their | <sup>r</sup> Binary representation |

|------------------------|--------------------|------------------------------------|

|------------------------|--------------------|------------------------------------|

| Decimal No. | Hexadecimal No. | Binary coded Hex. No |

|-------------|-----------------|----------------------|

| 0           | 0               | 0000                 |

| 1           | 1               | 0001                 |

| 2           | 2               | 0010                 |

| 3           | 3               | 0011                 |

| 4           | 4               | 0100                 |

| 5           | 5               | 0101                 |

*Hexadecimal System* groups numbers by 16 and power of 16.

| 6  | 6 | 0110 |

|----|---|------|

| 7  | 7 | 0111 |

|    |   |      |

| 8  | 8 | 1000 |

| 9  | 9 | 1001 |

| 10 | А | 1010 |

| 11 | В | 1011 |

| 12 | С | 1100 |

| 13 | D | 1101 |

| 14 | E | 1110 |

| 15 | F | 1111 |

### 1.4 NUMBER SYSTEM CONVERSION

As the computer uses different number systems, there is a process of converting generally used decimal number systems to other number systems and vice-versa.

#### 1.4.1 Binary to Decimal Conversion

To convert a binary number to its decimal equivalent we use the following expression. The weight of the n<sup>th</sup> bit of the number from right hand side

$= n^{th} bit \times 2^{n-1}$

First we mark the bit position and then we give the weight of each bit of the number depending on its position. The sum of the weight of all bits gives the equivalent number.

**Example 1.4 :** Convert binary  $(100101)_2$  to its decimal equivalent. **Solution :**  $(100101)_2 = 1 \times 2^5 + 0 \times 2^4 + 0 \times 2^3 + 0 \times 2^2 + 1 \times 2^0$

$$= 32 + 0 + 0 + 4 + 0 + 1$$

$$= 37$$

So,  $(100101)_2 = (37)_{10}$

Mixed number contain both integer and fractional parts and can convert to its decimal equivalent is as follows :

**Example 1.5 :** Converting (11011.101)<sub>2</sub> to its equivalent decimal no. **Solutaion :**

$$(11011.101)_{2} = (1 \times 2^{4} + 1 \times 2^{3} + 0 \times 2^{2} + 1 \times 2^{1} + 1 \times 2^{0}) + (1 \times 2^{-1} + 0 \times 2^{-2} + 1 \times 2^{-3}) = (16 + 8 + 0 + 1) + (0.5 + 0 + 0.125) = 27.625$$

So,  $(11011.101)_{2} = (27.625)_{10}$

#### 1.4.2 Decimal to Binary Conversion

There are different methods used to convert decimal number to binary numbers. The most common method is, repeatedly divide the decimal number to binary number by 2, then the remainders 0's and 1's obtained after division is read in reverse order to obtain the binary equivalent of the decimal number. This method is called **double-double method**.

**Example 1.6 :** Convert (75)<sub>10</sub> to its binary equivalent.

| Solution : | 2   <u>75</u> |     | Remainder |               |

|------------|---------------|-----|-----------|---------------|

|            | 2   <u>37</u> | LSB | 1         |               |

|            | 2   <u>18</u> |     | 1         |               |

|            | 2   <u>9</u>  |     | 0         | Read in       |

|            | 2 l <u>4</u>  |     | 1         | reverse order |

|            | 2   <u>2</u>  |     | 0         |               |

|            | 1             | MSB | 0         |               |

So, (75)<sub>10</sub> = (001011)<sub>2</sub>

**Example 1.7** : Convert decimal fraction  $(25.625)_{10}$  to its equivalent binary no.

| Solution : | 2  <u>25</u>           | Remainder                   | MSB              | 0.625      |

|------------|------------------------|-----------------------------|------------------|------------|

|            | 2   <u>12</u>          | 1                           |                  | <u>× 2</u> |

|            | 2   <u>6</u>           | 0                           |                  | 1.250      |

|            | 2   <u>3</u>           | 0                           |                  | <u>× 2</u> |

|            | 1                      | 1                           |                  | 0.500      |

| (25)       | ) <sub>10</sub> = (11) | 001) <sub>2</sub>           |                  | <u>× 2</u> |

|            |                        |                             |                  | 1.000      |

| (0.625)    | <sub>10</sub> = (0.1   | 01) <sub>2</sub>            |                  |            |

| So,        | (25.625                | 5) <sub>10</sub> = (11001.1 | 01) <sub>2</sub> |            |

Digital Logic

#### 1.4.3 Octal to Decimal Conversion

The method of converting octal numbers to decimal numbers is simple. The decimal equivalent of an octal number is the sum of the numbers multiplied by their corresponding weights.

Example 1.8 : Find decimal equivalent of octal number (153)<sub>8</sub>

**Solution :**  $1 \times 8^2 + 1 \times 8^1 + 1 \times 8^0 = 64 + 40 + 3 = 107$

So, (153)<sub>8</sub> = (107)<sub>10</sub>

The fractional part can be converted by multiplying it by the negative powers of 8 as shown in the following example.

Example 1.9 : Find decimal equivalent of octal number (123.21)<sub>8</sub>

**Solution :**  $(1X8^2 + 2X8^1 + 3X8^0) + (2 \times 8^1 + 1 \times 8^2)$

= (64 +16 + 3) + (0.25 + 0.0156) = 83.2656

So,  $(123.21)_8 = (83.2656)_{10}$

#### 1.4.4 Decimal to Octal Conversion

The procedure for conversion of decimal numbers to octal numbers is exactly similar to the conversion of decimal number to binary numbers except replacing 2 by 8.

Example 1.10 : Find the octal equivalent of decimal (3229)<sub>10</sub>

Solution :

Remainders

8 <u>I4121</u>

8

8 <u>I515</u>

1

▲ read from MSB

8 <u>I64</u>

3

to LSB

8 <u>I8</u>

0

1

1

0

0

So, (4121)<sub>10</sub>=(10031)<sub>8</sub>

The fractional part is multiplied by 8 to get a carry and a fraction as shown in the following example.

**Example 1.11 :** Find the octal equivalent of (.123)<sub>10</sub>

**Solution :** Octal equivalent of fractional part of a decimal number as follows :

Read the integer to the left of the decimal point.

The calculation can be terminated after a few steps if the fractional part does not become zero.

The octal equivalent of  $(0.123)_{10} = (0.0767)_8$

**NOTE :** The octal to binary and binary to octal conversion is very easy. Since, 8 is the third power of 2, we can convert each octal digit into its three-bit binary form and vice versa.

**Example 1.12 :** Convert (567)<sub>8</sub> to its binary form.

| Solution : | 5   | 6   | 7   |

|------------|-----|-----|-----|

|            | Ļ   | Ļ   | Ļ   |

|            | 101 | 110 | 111 |

So,  $(567)_8 = (101 \ 110 \ 111)_2$

Conversion from binary to octal is just opposit of the above example.

#### 1.4.5 Hexadecimal to Decimal Conversion

The method of converting Hexadecimal numbers to decimal number is simple. The decimal equivalent of an Hexadecimal number is the sum of the numbers multiplied by their corresponding weights.

**Example 1.13 :** Find the decimal equivalent of (4A8C)<sub>16</sub>

#### Solution :

$\begin{aligned} (4A8C)_{16} &= (4 \times 16^3) + (10 \times 16^2) + (8 \times 19^{1)} + (12 \times 16^0) \\ &= 16384 + 2560 + 128 + 12 \\ &= (19084)_{10} \\ (4A83)_{16} &= (19084)_{10} \end{aligned}$  Example 1.14 : Find the decimal equivalent of (53A.0B4)\_{16} \\ Solution :

$(53A.0B4)16 = (5 \times 16^{2}) + (3 \times 16^{1}) + (10 \times 16^{0}) + (0 \times 16^{-1}) + (11 \times 16^{-2}) + (4 \times 16^{-3})$

(53A.0B4)<sub>16</sub> =(1338.0439)<sub>10</sub>

#### 1.4.6 Decimal to Hexadecimal Conversion

The procedure for conversion from decimal no. and decimal fraction no. to hexadecimal equivalent is exactly similar to the conversion of decimal to binary no. except replacing 2 by 16.

**Example 1.15 :** Convert decimal  $(1234.675)_{10}$  to hexadecimal.

**Solution :** 1st consider (1234)<sub>10</sub>

|                                                          | Remainder                             |        |             |  |  |

|----------------------------------------------------------|---------------------------------------|--------|-------------|--|--|

|                                                          | Decimal                               | Hexad  | ecimal      |  |  |

| 16 <u> 1234</u>                                          | 2                                     | 2      |             |  |  |

| 16 <u> 77</u>                                            | 13                                    | D      |             |  |  |

| 16 <u>l4</u>                                             | 4                                     | 4      |             |  |  |

| (1234) <sub>10</sub> = (4D2                              | ) <sub>16</sub>                       |        |             |  |  |

| Conversion of (                                          | Conversion of (0.675) <sub>10</sub> : |        |             |  |  |

|                                                          | D                                     | ecimal | Hexadecimal |  |  |

| 0.675 × 16                                               | = 10.8                                | 10     | А           |  |  |

| 0.800 × 16 =                                             | = 12.8                                | 12     | С           |  |  |

| 0.800 × 16 =                                             | = 12.8                                | 12     | С           |  |  |

| 0.800 × 16 =                                             | = 12.8                                | 12     | С           |  |  |

| (0.675) <sub>10</sub> = (0.ACC) <sub>16</sub>            |                                       |        |             |  |  |

| Hence (1234.675) <sub>10</sub> = (4D2.ACC) <sub>16</sub> |                                       |        |             |  |  |

If the decimal number is very large, it is tedious to convert the number to binary directly. So it is always advisable to convert the number into hex first, and then convert the hex to binary.

## 1.5 COMPLEMENT OF NUMBERS

Complements are used in digital computers for simplifying the substraction operation and for logical manipulation. The complement a binary number is obtained by inverting itsall the bits.

For example, the complement of 10011 is 01100 and 00101 is 11010 etc. The complement again depends on the base of the number.

There are two types of complements for a number of base r. These are :

- r's complement and

- (r-1)'s complement,

For example, for decimal numbers the base is 10. Therefore, complements will be 10's complement and (10-1)=9's complement. For binary numbers, the complement are 2's complement and 1's complement since base is 2.

#### 1.5.1 (r-1)'s Complement

Giiven a number N in base r having n digits, the (r-1)'s complement of N is defined as  $(r^n-1) - N$ .

**9'sComplement :** For decimal numbers r=10 and r-1=9, so the 9's complement of N is  $(10^{n}-1) - N$ .

For example, with n = 4 we have  $10^4 = 10000$  and  $10^4-1 = 9999$ . It follows that the 9's complement of a decimal number is obtained by subtracting each digit from 9.

For example, 9's complement of 49 is (99–49) = 50 9's complement of 127 is (999–127) = 872

**1's Complement :** For binary numbers, r = 2 and (r-1) = 1, so the 1's complement of N is  $(2^n-1) - N$ . Again,  $2^n$  is represented by a binary number that consists of a 1 followed by n 0's.  $2^n-1$  is a binary number represented by n 1's. For example, with n = 4, we have  $2^4 = (10000)_2$  and  $2^4-1 = (1111)_2$ . Thus the 1's complement of a binary number is obtained by subtracting each digit from 1.

However, the subtraction of a binary digit from 1 causes the bit to change from 0 to 1 or from 1 to 0. Therefore, the 1's complement of a binary number is formed by changing 1's into 0 and 0's into 1's. For example, 1's complement of 1010111 is 0101000.

#### 1.5.2 r's Complement

The r's complement of a n-digit number N in base r is defined as  $r^n - N$  for N =0 and 0 for N = 0. Comparing with the (r-1)'s complement, we note that the r's complement is obtained by adding 1 to the (r-1)'s complement.

**10's Complement :** The 10's complement of a decimal number is equal to the 9's complement of the number plus 1

i.e. 10's complement of decimal number = Its 9's complement +1

So, 10's complement of 49 is (99–49) + 1 = 50 + 1 = 51

10's complement of 127 is (999–127) + 1 = 872 + 1 = 873

The 7's and 15's complement of a number is found by subtracting each digit of the number from 7 and 15 respectively.

Like 8's complement and 16's complement of a number is found by adding 1 to the LSB of the 7's and 15's complement of an octal and hexadecimal number respectively. **2's Complement :** It is obtained by adding 1 in the 1's complement form of the binary numbers.

i.e. 2's complement of binary number = 1's complement of that number + 1

For example, 2's complement of 1010111 is 0101000 + 1 = 0101001

## **1.6 DATA REPRESENTATION**

Data are usually represented by using the alphabets A to Z, numbers 0 to 9 and various other symbols. This form of representation is used to formulate problem and fed to the Computer. The processed output is required in the same form. This form of representation is called *external data representation*. However, the computer can understand data only in the form of 0's and 1's. The method of data representation in a form suitable for storing in the memory and for processing by the CPU is called the internal data representation on digital computer.

Data, in general, are of two types : Numeric and non-numeric (Character data). The numeric data deals only with numbers and arithmatic operations and non numeric data deals with characters, names addresses etc. and non-arithmatic operations.

#### 1.6.1 Fixed Point Representaion

A fixed point numbers in binary system uses a sign bit. A positive number has a sign bit 0 while the negative number has a sign bit 1. A negative number can be represented in one of the following ways.

- Signed magnitude representaion

- Signed 1's complement representaion

- Signed 2's complement representaion

Assume that the size of the register is 7 bit and the 8<sup>th</sup> position bit in used for error checking and correction or other purposes.

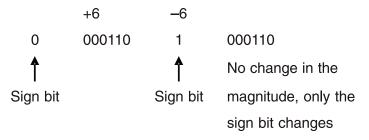

#### a) Signed magnitude representation

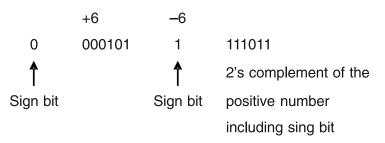

#### b) Signed 1's complement representation

|   | +6     | -6 |        |

|---|--------|----|--------|

| 0 | 000110 | 1  | 111001 |

Here 0 and 1 are sign bits. 1's complement is getting for the –ve integer is by taking complement of all the bits of +ve no. including sign bit.

#### c) Signed 2's complement representation

The signed magnitude system is easier to interpret but computer arithmatic with this is not efficient. The circuits for handling numbers are simplified if 1's or 2's complement systems are used and as a result one of these is almost always adopted. **Note 1 :** In 1's and 2's complements, all positive integers are represented as sign magnitud system.

**Note 2 :** When all the bits of the computer word are used to represent the number and no bit is used for signed representation, it is called unsigned representation of the number.

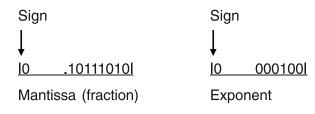

#### 1.6.2 Floating Point Representation

A number which has both an integer part as well as a fractional part is called real number or floating point number. A floating point number is either positive or negative. Examples of real decimal numbers are 156.65, 0.893, -235.75, -0.253 etc. Examples of binary real numbers are 101.101, 0.11101, -1011.101, -0.1010 etc.

The first part of the number is a fixed point number which is called mantissa. It can be an integer or a fraction.

The second part specifies the decimal or binary point position and is termed exponent. It is not a physical point. Therefore, whenever we are representing a point and is termed as an exponent. It is only the assumed position. For example, for decimal o. +15.37, the typical floating point notaion is :

$51.47 = 0.5147 \times 10^2$  or  $5147 \times 10^{-2}$

Now, The floating point representation of  $0.5147 \times 10^3$  is :

| Sign                                                           | Sign                          |  |  |

|----------------------------------------------------------------|-------------------------------|--|--|

| Ļ                                                              | Ļ                             |  |  |

| <u>l0 .51471</u>                                               | <u>10 021</u>                 |  |  |

| Mantissa (fraction)                                            | Exponent                      |  |  |

| The floating point representation                              | of 5147 X 10 <sup>-2</sup> is |  |  |

| Sign                                                           | Sign                          |  |  |

| Ļ                                                              | Ļ                             |  |  |

| <u>l0 51471</u>                                                | <u>10 021</u>                 |  |  |

| Mantissa (Integer)                                             | Exponent                      |  |  |

| Similarly for example a floating point binary number 1011.1010 |                               |  |  |

| can be represented as : $1011.1010 = 0.10111010 \times 2^4$    |                               |  |  |

This can be represented in a 16 bit register as follows

The mantissa occupies 9 bits (1 bit for sign and 8 bits for value) and the exponent 7 bits (1 bit for sign and 6 bits for value). The binary point (.) is not physically indicated in the register, but it is only assumed (position) to be there.

In general form, the floating point numbers is expressed as :

$\mathsf{N}=\mathsf{M}\;\mathsf{X}\;\mathsf{R}^{\mathrm{e}}$

Where, M-Mantissa

R - Radix (or base)

e - Exponent

The mantissa M and exponent e are physically present in register. But the radix R and the point (decimal or binary point) are not indicated in the register. There are only assumed for computation and manipulation.

**Normalized Floating point Number :** Floating point numbers are often represented in normalized forms. A floating point number where mantissa does not contain zero as the most significant digit of the number is considered to be in normaliged form. For example,  $0.00038695 \times 10^5$  and  $0.0589 \times 10^{-4}$  are not normaliged numbers. But  $0.38695 \times 10^2$  and  $0.589 \times 10^{-5}$  are normaliged numbers. Similarly, for binary number also,  $0.0011001 \times 2^8$  and  $0.0001011 \times 2^{-5}$  are not non-normaliged binary numbers. But  $0.11001 \times 2^6$  and  $0.1011 \times 2^{-8}$  are normaliged binary numbers.

A zero cannot be normaliged as all the digits in the mantissa is zero.

Arithmatic operations involved with floating point numbers are more complex. It takes larger time for execution and requires complex hardware. But floating point representation is frequently used in scientific calculations. **Overflow and Underflow :** When the result is too small to be presented by the computer, an overflow or underflow condition exists. When two floating-point numbers of the same sign are added, a carry may be generated out of high-order bit position. This is known as mantissa overflow. In case of addition or subtraction floating point numbers are aligned. The mantissa is shifted right for the alignment of a floating point number. Sometimes, the low order bits are lost in the process of alignment. This is referred as mantissa underflow. To perform the multiplication of two floating point numbers, the exponents are added. In certain cases the sum of the exponents maybe too large and it may exceed the storing capacity of the exponent field. This is called exponent overflow. In case of division the exponent of the divisior is subtracted from the exponent of the dividend. The result of subtraction may be too small to be represented. This is called exponent underflow.

Overflow or underflow resulting from a mantissa operation can be corrected by shifting the mantissa of the result and adjusting the exponent. But the exponent overflow or underflow can not be corrected and hence, an error indication has to be displayed on the computer screen.

## **1.7 BINARY ARITHMATIC**

#### 1.7.1 Addition

Binary addition is performed in the same manner as decimal addition. Since, in binary system only two digit 0s and 1s are used, the addition will be like-

0 + 0 = 0

0 + 1 = 1 = 1 + 0

1 + 1 = 0, Carry 1 to the next left column

1 + 1 + 1 = 1, Carry 1 to the next column.

Carry overs are performed in the same manner as in decimal arithmetic.

Example 1.16 : Add the binary numbers

(i) 1011 and 1001

(ii) 10.011 and 1.001

#### Solution :

| (i)  | Binary no.   |       | Equivalent decimal no. |

|------|--------------|-------|------------------------|

|      | 11           | carry |                        |

|      | 1011         |       | 11                     |

|      | <u>+1001</u> |       | _9                     |

|      | 10100        |       | 20                     |

| (ii) | 10.011       |       | 2.375                  |

|      | <u>1.001</u> |       | <u>1.125</u>           |

|      | 11.100       |       | 3.500                  |

Since the circuit in all digital systems actually can handle two numbers to performs addition, it is not necessary to consider the addition of more than two binary numbers. When more than two numbers to be added, the first two are added first and then their sum is added to the third and so on.

The complexity may rise when to add combination of positive and negative binary number. In this case the arithmatic addition is dependent on the representation of

- a) Signed magnitude

- b) Signed 1's complement

- c) Signed 2's complement

This will be more clear if we discuss through the following example:

**Example 1.17 :** Add 25 and -30 in binary using 7 bit register in signed magnitude representation

- a) Signed 1's complement representaion

- b) Signed 2's complement representaion

**Solution :** Here, 25 is +25 = 0011001 in binary system

-30 = 1011110 in binary system

To do the arithmatic addition with one negative number we have to check the magnitude of the numbers. The number having smaller magnitude is there subtracted from the bigger number and the sign of bigger number is selected. To implement such a scheme in digits, hardware will require a long sequence of control decisions as well as circuits that will add, compare and subtract numbers. The better attentative of arithmatic with one negative number is signed 2's complement.

#### In signed 2's complement representation :

| We                                                                | e get that | +30 is   | 0          | 01       | 1110       |              |      |         |

|-------------------------------------------------------------------|------------|----------|------------|----------|------------|--------------|------|---------|

|                                                                   |            | –30 is   | 1          | 01       | 1110       |              |      |         |

| Nc                                                                | w, 2's com | plement  | of         | -30      | (includir  | ng sign bit) | 1    | 100010  |

|                                                                   |            |          |            | +25      | is         |              | 0    | 011001  |

| Ad                                                                | ldition    |          |            |          |            |              |      |         |

|                                                                   | +25        | 0        | 01         | 1        | 001        |              |      |         |

|                                                                   | <u>–30</u> | <u>1</u> | <u>100</u> | <u>)</u> | <u>010</u> |              |      |         |

|                                                                   | 05         | 1        | 111        | l        | 011 (      | Just add th  | ie n | umbers) |

| The result for negative number will store n signed 2's complement |            |          |            |          |            |              |      |         |

| form. So the above result in signed 2's complement form. So the   |            |          |            |          |            |              |      |         |

| above result in signed 2's complemnt form including sign bit is   |            |          |            |          |            |              |      |         |

1 000 100 +1 = 1 000 101 Which is -05 in decimal system. From the above example it is noticed that, signed 2's complement representation is simpler than signed magnitude representation. This procedure requires only one central decision and only one circuit for adding the two numbers. But it puts additional condition that the negative numbers should be stored in signed 2's complement form in the register. This can be achieved by complementing the positive number bit by bit then incrementing the resultant by 1 to get signed 2's complement.

**In signed 1's complement representation :** This method is also simple. The rule is taht, add the two numbers including the sign bit. If carry of the most significant bit or sign bit is one, then increment the result by 1 and discard the carry over.

Addition :

$+25 = 0 \quad 011 \ 001$  $-30 = 1 \quad 100 \ 001 \ (1's complement of -30)$  $-5 = 1 \quad 111 \ 010$

The result will store in 1's complement format. So, 1111 010 in 1's complement format including the sign bit is 1 000 101 which is the required result.

Example 1.18 : Add -25 and +30 using 7-bit register.

#### Solution :

```

-25

1

100

110 (1's complement of 25)

+30

0

011

110

+5

10

000

100

Carry bit, so add 1 to the sum and discard the carry.

This sum is now = 0 000 101 which is +5

Example 1.19 : Add –25 and –30 using 7-bit register.

Solution : -25

100

1

110 (1's complement of 25)

-30

1

<u>100</u>

<u>001</u> (1's complement of 30)

-55 11

000

111

Carry bit, so add 1 to sum and discard the carry.

```

Now the sum is = 1 001 000, which is -55 Since, +55 is 0 110 111

So, -55 is in 1's complement 1 001 000

The interesting feature about these representation is the representation of 0 in signed magnitude and 1's complement. There are two representation for zero are :

| Signed magnitude      | +0 |        | -0 |        |

|-----------------------|----|--------|----|--------|

|                       | 0  | 000000 | 1  | 000000 |

| Signed 1's complement | 0  | 000000 | 1  | 111111 |

But in signed 2's complement, there is just one zero and there are no positive or negative zero.

+0 000000

| -0 | in 2's complement is +0 | = | 1     | 111111 |

|----|-------------------------|---|-------|--------|

|    |                         |   |       | 1      |

|    | 1                       |   | 0     | 000000 |

|    | 1                       |   |       |        |

|    | - 11 -                  |   | 11-1- |        |

discard this carry

Thus, both +0 and –0 are same in 2's complement notaton. This is an *added advantage* in favour of 2's complement notation. The maximum number which can be accomodated in registers also depends on the type of representation. In general, in a 8 bit register 1 bit is used as sign. Therefore, the rest of 7 bit are used for representing the value. The value of maximum and minumum number which can be represented are :

For signed magnitude representation  $2^7 - 1$  to  $-(2^7 - 1)$

= 128 -1 to - (128-1) = 127 to - 127,

which is for signed 1's complement representation. For signed 2's complement representation is from + 127 to -128. The -128 is represented in signed 2's complement notation as 10000000.

#### 1.7.2 Subtraction

Though there are other method of performing subtraction, we will consider the method of subtraction known as complementary subtracton. This is a more efficient method of subtraction while using electronics circuits. The following three steps have to follow to subtract binary numbers.

#### In 1's complement method :

- 1. Find the 1's complement of the number which is subtracting.

- 2. Add the number which is subtracting from with the complement value obtained from step 1.

- 3. If there is a carry of 1, add the carry with the result of addition. Else, take complement again of the result and attach a negative sign with the result.

**Example 1.20 :** Subtract 5 – 6 by 1's complement method.

Solution: 5 Binary equivalent is 101

6 Binary equivalent is 110

Step 1 : 1's complement of 6 is 001

Step 2 : Adding 001 with 101 give the result as

```

001

<u>+ 101</u>

```

```

110

```

Step 3 : Since there is no carry in step 2, we take the complement again which will be 001 and after attaching negative sign the required result will be –001 which is -1.

**In 2's complement method :** It is same as 1's complement method except the step 3. The steps are :

Step 1 : Find the 2's complement of the number which is subtracting.

Step 2 : Add the number which is subtracting from with the comple ment value obtained from step 1.

Step 3 : If there is a carry of 1, Ignore it. Else, take 2's complement of the result again and attach a negative sign with the result.

Example 1.21 : Subtract 5 – 7 by 2's complement method.Solution :5Binary equivalent is1017Binary equivalent is111Step 1 : The 2's complement of 7 is 000 + 1 = 001Step 2 : Adding 001 with 101 will give result as :001101110(No carry)

Step 3 : Since no carry, the 2's complement of 110 is 001 + 1 = 010 and attaching a negative sign the required result is -10.

**Overflow** : An overflow is said to have occured when the sum of two n digits number occupies (n+1) digits. This definition is valid for both binary as well as decimal digits. But what is the significance of overflow for binary numbers since it is not a problem for the cases when we add two numbers? Well, the answer lies in the limits or representation of numbers. Every computer employs a limit for representation number eg. in our examples we are using 8 bit registers of calculating the sum. But what will happen if the sum of the two numbers can be accommodated in 9 bits? Where are we going to store the 9th bit? The problem will be more clear by the following example. In case of a +ve no. added to a –ve no., the sum of result will always be smaller than the two numbers. An overflow always occurs when the added nos. are both +ve or both -ve.

**Example 1.22**: Add the numbers 65 and 75 in 8 bit register in signed 2's complement notation.

Solution : 65 0 1000001 75 0 1001011

140 1 0001100

This is a -ve number and the 2's complement of teh result is equal to -115 which obvious is a wrong result. This has occured because of overflow.

Detection of Overflow : Overflow can be detected as :

If the carry out of the MSBs of number (or, carry into the sign bit) is equal to the carry out of the sign bit then overflow must have occured. For example

| -65         | 1      | 01111   | 11    | -65       | 1      | 0111   | 111  |

|-------------|--------|---------|-------|-----------|--------|--------|------|

| -15         | 1      | 11100   | 01    | -75       | 1      | 0110   | 101  |

| -80         | 11     | 01100   | 000   | -140      | 10     | 1110   | 100  |

| Carry       |        | =       | 1     | Carry     |        |        | = 10 |

| Carry from  | m MS   | В =     | 1     | Carry f   | rom M  | ISB    | = 0  |

| Carry from  | m sigr | n bit = | 1     | Carry f   | rom si | gn bit | = 1  |

| Sign bit is | 3      | =       | 1     | Sign bi   | it is  |        | = 0  |

| No overfl   | ow     | TI      | neref | ore, over | low    |        |      |

Thus, overflow has occured, i.e. the arithmatic results so calculated have exceeded the capacity of the representation. This overflow also implies that the calculated results might be erronous.

#### 1.7.3 Multiplication

Multiplication in binary follow the same rules that are followed in the decimal system. The table to be remembered is :

```

0 \times 0 = 0 \qquad 1 \times 0 = 0

0 \times 1 = 0 \qquad 1 \times 1 = 1

For example, multiplying 10101 × 11001

10101

× 11001

10101

10101

1000001101

```

#### 1.7.4 Division

The process of binary division is same as the decimal long division. In binary division we have:

0/1 = 0 1/1 = 1

The steps for binary division are :

- 1. Start from the left of the divided.

- 2. Perform subtraction in which the divisor is subtracted from the divedend.

- a) If subtraction is possible put a 1 in the quotient and subtract the divisor from the corresponding digits of the dividend put a 0 in the quotent

- b) Bring down the next digit to the right of the remainder.

- 3. Execute step 2 till there are no more digits left to bring down from the dividend.

Example 1.23 : Divide 1011001 by 110

#### Solution :

|           | <u>0111</u>  | (Quotient) |  |  |

|-----------|--------------|------------|--|--|

| (Divisor) | 110  1011001 | (Dividend) |  |  |

|           | <u>110</u>   |            |  |  |

|           | 1010         |            |  |  |

|           | <u>110</u>   |            |  |  |

|           | 1000         |            |  |  |

|           | <u>110</u>   |            |  |  |

|           | 0101         |            |  |  |

Here 111 is teh answer and 101 is the Remainder.

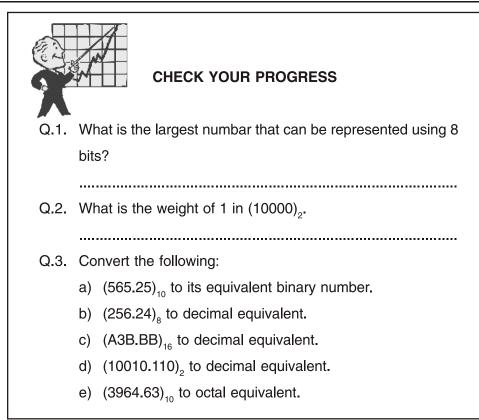

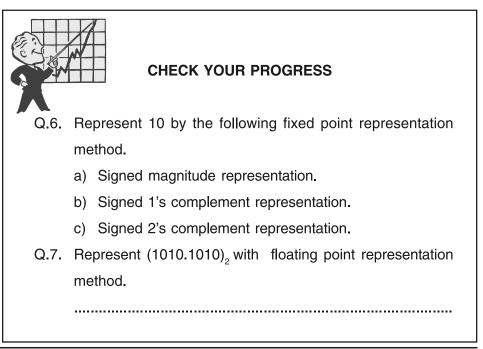

|       | CHECK YOUR PROGRESS                                                             |

|-------|---------------------------------------------------------------------------------|

| Q.8.  | Add 35 and -40 in binary using 7 bit register in 2's complement representation. |

| Q.9.  | Add binary no. 110011.010 and 1000.10                                           |

| Q.10. | Subtract $(1010101)_2$ - $(1001001)_2$ by 2's complement method.                |

| Q.11. | Multiply (11001) <sub>2</sub> by (101) <sub>2</sub> .    |

|-------|----------------------------------------------------------|

| Q.12. | Divide (101101.101) <sub>2</sub> by (110) <sub>2</sub> . |

|       |                                                          |

. .

## **1.8 COMPUTER CODES**

A **code** is a symbol or group of symbols that represents discrete elements. Coding of characters has been standardised to enable transfer of data between computers. *Numeric data* is not the only form of data handled by a computer. We often require to process *alphanumeric data* also. An alphanumeric data is a string of symbols, where a symbol may be one of the letters A, B, C, ...., Z, or one of the digits 0, 1, 2, ...., 9, or a special character, such as + - \*/, . () = (space for blank)etc. However, the bits 0 and 1 must represent any data internally. Hence, computers use binary coding schemes to represent data internally. In binary coding, a group of bits represent a symbol is called a *byte*. To indicate the numbers of bits in a group, sometimes a byte is referred to as "n-bit byte", where the group contains n bits. However, the term "byte" commonly means an 8-bit byte because most modern computers use 8 bits to represent a symbol.

#### 1.8.1 BCD

In computing and electronic systems, **Binary-Coded Decimal** (**BCD**) is a way to express each of the decimal digits with a binary code. Its main virtue is that it allows easy conversion to decimal digits for printing or display and faster decimal calculations. Decimal numbers with their BCD equivalent are given in the table 2.4 :

| Table 2.4. DCD Coue |      |  |  |

|---------------------|------|--|--|

| Decimal             | BCD  |  |  |

| 0                   | 0000 |  |  |

| 1                   | 0001 |  |  |

| 2                   | 0010 |  |  |

| Table 2.4 : BCD Co | de |

|--------------------|----|

|--------------------|----|

| _ |   |      |

|---|---|------|

| Γ | 3 | 0011 |

|   | 4 | 0100 |

|   | 5 | 0101 |

|   | 6 | 0110 |

|   | 7 | 0111 |

|   | 8 | 1000 |

|   | 9 | 1001 |

Unlike binary encoded numbers, BCD encoded numbers can easily be displayed by mapping each of the nibbles(4-bits) to a different character. Conversion of decimal to BCD and BCD to decimal are shown below:

**Example 1.24 :** Convert the decimal numbers 47 and 180 to BCD.

**Solution :** 4 = 0100 and 7 = 111

47 = 0100111

Similarly, 180=0001 1000 0000

**Example 1.25**: Convert each of the BCD code 1000111 to decimal. **Solution**: First we have to divide the whole BCD code by a set of 4bits from right to left. Then from left to right we can put the corresponding decimal numbers.

> 0100 0111 4 7

Thus, 1000111(in BCD) = 47 (in Decimal)

**BCD addition :** BCD is a numeric code and can be used in arithmetic operations. Addition is the most important operation because the other three operations (subtraction, multiplication, and division) can be accomplished by the use of addition. Here is how to add two BCD numbers:

- Step1 : Add the two BCD numbers, using the rules for binary addition.

- Step 2 : If a 4-bit sum is equal to or less than 9, it is a valid BCD number.

- Step 3 : If a 4-bit sum is greater than 9, or if a carry out of the 4-bit group is generated, it is an invalid result. Add 6(0110) to

the 4-bit sum in order to skip the six invalid states and return the code to 8421. If a carry results when 6 is added, simply add the carry to the next 4-bit group.

Example 1.26 : Add the following BCD numbers :

- a) 0001 + 0100

- b) 10000111 + 01010011

Solution : The decimal number addition are shown for comparison.

| (a)                                                                | 0001         | 1            |                                  |  |  |  |

|--------------------------------------------------------------------|--------------|--------------|----------------------------------|--|--|--|

| <u>+0100</u>                                                       |              | <u>+4</u>    |                                  |  |  |  |

| 0101                                                               |              | 5            |                                  |  |  |  |

| $\therefore$ 0001 + 0100 = 0101 Which is valid BCD no. (Value < 9) |              |              |                                  |  |  |  |

| (b)                                                                | 1000         | 0111         | 87                               |  |  |  |

|                                                                    | <u>+0101</u> | <u>0011</u>  | <u>+ 53</u>                      |  |  |  |

|                                                                    | 1101         | 1010         | Both groups are invalid (>9)+140 |  |  |  |

|                                                                    | <u>+0110</u> | <u>+0110</u> | Add 6 (i.e.,0110) to both groups |  |  |  |

| 00                                                                 | 01 0100      | 0000         | Valid BCD number which is 140    |  |  |  |

|                                                                    |              |              | in decimal.                      |  |  |  |

#### 1.8.2 ASCII

ASCII stands for American Standard Code for Information Interchange. It is a very well-known fact that computers can manage internally only 0s (zeros) and 1s (ones). By means of sequences of 0s and 1s the computer can express any numerical value as its binary translation, which is a very simple mathematical operation.

However, there is no such evident way to represent letters and other non-numeric characters with 0s and 1s. Therefore, in order to do that, computers use *ASCII tables*, which are tables or lists that contain all the letters in the roman alphabet plus some additional characters. In these tables each character is always represented by the same order number. For example, the ASCII code for the capital letter "A" is always represented by the order number 65, which is easily representable using 0s and 1s in binary: 65 expressed as a binary number is 1000001. ASCII has 128 character codes(from 0 to 127) and symbols represented by a 7-bit binary code.

ASCII is the common code for microcomputer equipment. The first 32 characters in the ASCII-table are unprintable control codes and are used to control peripherals such as printers. Examples of the control characters are "NULL", "line feed", "start of text" and "escape". The other characters are graphic symbols that can be printed or displayed and that include the letters of the alphabet (lowercase and upper case), the ten decimal digits, punctuation signs, and other commonly used symbols.

#### 1.8.3 EBCDIC

EBCDIC is the abbreviation for **Extended Binary-Coded Decimal Interchange Code**. EBCDIC is an IBM code for representing characters as numbers. It uses 8 bits per character. Thus 256 charaters can be represented with 8 bits. The 9th position bit can be used for parity. The EBCDIC code is used in IBM mainframe models and other similar machines.

In EBCDIC, the first 4 bits are known as zone bits and remaining 4 bits represent digit values. Electronic circuits are available to transform characters from ASCII to EBCDIC and vice-varsa.

#### 1.8.4 Gray Code

The gray code is an unweighted code not suited for arithmatic operations, but useful for input output devices, analog to digital converters etc. The **Gray code**, named after *Frank Gray*, is a binary numeral system where two successive values differ in only one digit. It is sometimes referred to as reflected binary, because the first eight values compare with those of the last 8 values, but in reverse order.

The Gray code was originally designed to prevent spurious output from electromechanical switches. Today, Gray codes are widely used

to facilitate error correction in digital communications such as digital

terrestrial television and some cable TV systems.

| Decimal | Gray Code | Binary |  |

|---------|-----------|--------|--|

| 0       | 0000      | 0000   |  |

| 1       | 0001      | 0001   |  |

| 2       | 0011      | 0010   |  |

| 3       | 0010      | 0011   |  |

| 4       | 0110      | 0100   |  |

| 5       | 0111      | 0101   |  |

| 6       | 0101      | 0110   |  |

| 7       | 0100      | 0111   |  |

| 8       | 1100      | 1000   |  |

| 9       | 1101      | 1001   |  |

| 10      | 1111      | 1010   |  |

| 11      | 1110      | 1011   |  |

| 12      | 1010      | 1100   |  |

| 13      | 1011      | 1101   |  |

| 14      | 1001      | 1110   |  |

| 15      | 1000      | 1111   |  |

| Table | 2.5: | Gray | Code |

|-------|------|------|------|

|-------|------|------|------|

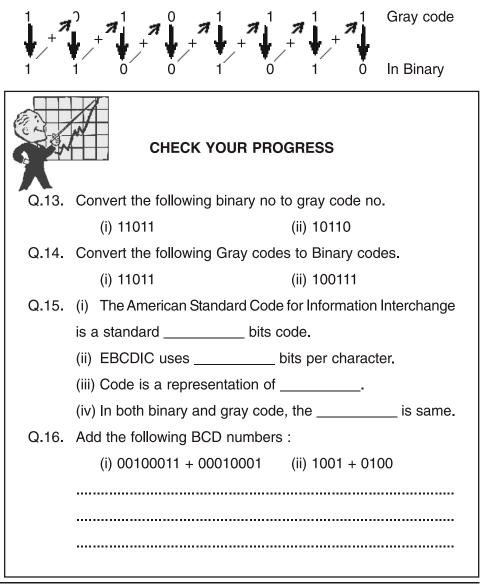

**Conversion from Binary to Gray code :** The following rules explain how to convert from a binary number to a Gray code :

- a) The most significant bit (left most) in the gray code is the same as the corresponding most significant bit in the binary code.

- b) Going from left to right, add each pair of adjacent pair of binary code to get the next Gray code bit. Discard carries.

For example, the conversion of the binary number 1100 to gray code is as follows:

Binary code 1 1 0 0

MSB (Most significant bit) LSB (Least significant bit)

MSB of Gray code will be same as MSB of Binary code. Here, it

will be 1.

Now , addition of each pair of adjacent bits of Binary code:

1 + 1 = 10 = 0, discarding the carry 1

- 1 + 0 = 1, no carry

- 0 + 0 = 0, no carry

- ... 1100 in gray code is 1010

Conversion from Gray to Binary code : The following rules apply:

- a) The most significant bit (left most) in the binary code is the same as the corresponding most significant bit in the gray code.

- b) Add each binary code bit generated by Gray code bit in the next adjacent position. Discard carries.

For example, binary 10101111 in gray code will be like this :

## 1.9 LET US SUM UP

- We have learnt 4 different number systems used in digital systems, their use, conversion of one number system to an other and the arithmatic operation of binary system. We also have learnt about the representation of data.

- In our day-to-day life, we use the decimal number system. In this system, base is equal to 10.

- The 1's complement of a binary number is formed by changing 1's into 0 and 0's into 1's

- The 2's complement of a binary number is obtained by adding 1 in the 1's complement form of the binary number.

- BCD, ASCII, EBCDIC, and Gray Code are the commonly used commputer codes.

# 1.10 ANSWERS TO CHECK YOUR PROGRESS

| Ans. to Q. No. 1 :  | (1111 1111) <sub>2</sub>                                                            |

|---------------------|-------------------------------------------------------------------------------------|

| Ans. to Q. No. 2 :  | Weight is $2^4 = 16$                                                                |

| Ans. to Q. No. 3 :  | a) (1000110101.01) <sub>2</sub> b) (174.44) <sub>10</sub> c) (2620.8) <sub>10</sub> |

|                     | d) (18.75) <sub>10</sub> e) (7574.50) <sub>8</sub>                                  |

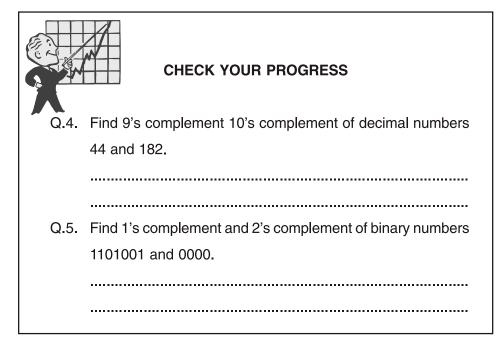

| Ans. to Q. No. 4 :  | 9's complement of 44 is 55 and 182 is 817                                           |

|                     | 10's complement of 44 is 56 and 182 is 818                                          |

| Ans. to Q. No. 5 :  | 1's complement of 1101001 is 0010110 and 0000 is 1111                               |

|                     | 2's complement of 1101001 is 0010111 and 0000 is 10000                              |

| Ans. to Q. No. 6 :  | a) 1 001010 b) 1 110101 c) 1 110110                                                 |

| Ans. to Q. No. 7 :  | Mantissa 10101010, fraction 000100 (in 16 bit                                       |

|                     | representation)                                                                     |

| Ans. to Q. No. 8 :  | (000101) <sub>2</sub>                                                               |

| Ans. to Q. No. 9 :  | (111011.110) <sub>2</sub>                                                           |

| Ans. to Q. No. 10 : | (1100) <sub>2</sub>                                                                 |

| Ans. to Q. No. 11 : | (1111101) <sub>2</sub>                                                              |

| Ans. to Q. No. 12 : | (111.10011) <sub>2</sub>                                                            |

| Ans. to Q. No. 13 : (i) 10110    | (ii) 11101                             |

|----------------------------------|----------------------------------------|

| Ans. to Q. No. 14 : (i) 10010    | (ii) 111010                            |

| Ans. to Q. No. 15 : (i) 7        | (ii) 8 (iii) Discrete elements         |

| (iv) MSB-b                       | Dit                                    |

| Ans. to Q. No. 16 : (i) Solution | ı:                                     |

| 0010                             | 0011 35                                |

| <u>+0001</u>                     | <u>0001</u> <u>+17</u>                 |

| 0011                             | 0100 +52 Valid BCD no. (since both <9) |

| (ii) Solution                    | n :                                    |

| 1001                             | 9                                      |

| <u>+0100</u>                     | <u>+4</u>                              |

| 1101                             | Invalid BCD number (>9) +13            |

| <u>+0110</u>                     | Add 6 (i.e., 0110)                     |

| 0001 0011                        | A valid BCD number which               |

|                                  | is 13 in decimal                       |

# 1.11 FURTHER READINGS

- Computer Fundamentals Architecture and Organization, B. Ram, New Age International (P) Ltd.

- Introduction to Computer Science, ITL Education Solution Limited, Pearson Education

- Digital Logic and Computer Design, M. M. Mano, PHI

- Computer Fundamentals, P K Sinha, BPB Publication.

- Digital Techniques, Dr. Pranhari Talukdar, N.L. Publications.

- *Computer Fundamentals and C programming*, Rath, Jagdev and Swain, SCITECH.

Q1. What is binary number system? How do you perform binary subtraction using 1's and 2's complement method?

| Number Systems |                                                                       |                      |               |                    |                   |                |                        |

|----------------|-----------------------------------------------------------------------|----------------------|---------------|--------------------|-------------------|----------------|------------------------|

| Q.2.           | What is meant by 'Base' or 'radix' of a number system?                |                      |               |                    |                   |                |                        |

| Q.3.           | What is a floating point number? What are the advantages of it?       |                      |               |                    |                   |                |                        |

| Q.4.           | What                                                                  | do you understa      | and by        | normali            | zed floatin       | ig p           | oint number?           |

| Q.5.           | Conve                                                                 | ert the decimal n    | umber         | s 15, 27           | 75 to BCD         |                |                        |

| Q.6.           | Add th                                                                | ne two BCD nun       | nbers 1       | 000011             | 1 and 010         | 100            | 011.                   |

| Q.7.           | Find 8                                                                | 's and 16's com      | plemer        | nt of the          | following         | :              |                        |

|                | (i)                                                                   | 67                   |               |                    | (ii) 5672         |                |                        |

| Q.8.           | Find th                                                               | ne 7's and 15's      | comple        | ment of            | f the follov      | ving           | <b>j</b> :             |

|                | (i)                                                                   | 643                  |               |                    | (ii) 15AB         |                |                        |

| Q.9.           | Write                                                                 | BCD for the foll     | owing a       | decimal            | number:           |                |                        |

|                | (i)                                                                   | 679                  |               |                    | (ii) 45.96        |                |                        |

| Q.10.          | Perfor                                                                | m the following      | with bi       | nary ari           | thmetic:          |                |                        |

|                | (i)                                                                   | 110111 + 1001        | 1             | (ii)               | 1110.001          | +              | 1010.101               |

|                | (iii)                                                                 | 11111 – 1101         |               | (iv)               | 1010.001          | - <sup>-</sup> | 110.1                  |

|                | (v)                                                                   | 1101 x 101           |               | (vi)               | 1011.11           | x 1.           | 1                      |

|                | (vii)                                                                 | 10011 / 111          |               | (viii)             | 101101.1          | 10             | 1 / 11.1               |

| Q.11.          | Conve                                                                 | ert the following    | to its b      | inary ec           | quivalent:        |                |                        |

|                | (i)                                                                   | (67) <sub>8</sub>    | (ii)          | (A8D) <sub>1</sub> | 6 (               | iii)           | (81B6.F) <sub>16</sub> |

|                | (iv)                                                                  | (64.3) <sub>10</sub> | (v)           | (765.4             | 5) <sub>8</sub> ( | vi)            | (1725.23) <sub>8</sub> |

| Q.12.          | Conve                                                                 | ert the following    | decima        | al numb            | er to octal       | nu             | mber:                  |

|                | (i)                                                                   | 104                  | (ii) 4        | 57                 | (i                | ii) 7          | 7562                   |

| Q.13.          | Conve                                                                 | ert the following b  | oinary n      | umbers             | to Octal a        | nd t           | ehn Hexadecimal        |

|                | equivalent:                                                           |                      |               |                    |                   |                |                        |

|                | (i)                                                                   | 1101101101           | (ii) <b>1</b> | 010110             | .001 (i           | ii) 1          | 101.1011               |

| Q.14.          | Convert the following decimal numbers to octal and then to its binary |                      |               |                    |                   |                |                        |

|                | equiva                                                                | alent:               |               |                    |                   |                |                        |

|                | (i)                                                                   | 100                  | (ii) 0        | .57                | (i                | ii) 1          | 011.3                  |

| Q.15.          | Perfor                                                                | m the following      | by 2's        | comple             | ment meth         | nod            | :                      |

|                |                                                                       |                      |               |                    |                   |                |                        |

(i) 10101 – 11011 (ii) 100011 – 1111

# UNIT 2 : BOOLEAN ALGEBRA

## UNIT STRUCTURE

- 2.1 Learning Objective

- 2.2 Introduction

- 2.3 Boolean Operators

- 2.4 Basic Theorems and Postulates of Boolean Algebra

- 2.5 Representation of Boolean Expression

- 2.6 Simplification of Boolean Functions

- 2.6.1 Algebric Manipulation Method

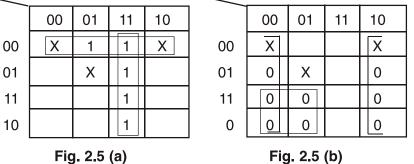

- 2.6.2 Map method

- 2.6.3 Don't Care Conditions

- 2.7 Let Us Sum Up

- 2.8 Further Readings

- 2.9 Answers to Check Your Progress

- 2.10 Model Questions

## 2.1 LEARNING OBJECTIVES

After going through this unit, you will be able to :

- Define Boolean Algebra

- Explain basic concepts of Boolean Algebra

- Define the basic theorems and postulates of Boolean Algebra

- Define Boolean function

- Define canonical and standard forms

- Simplify a Boolean function by algebric manipulations and Kmaps.

## 2.2 INTRODUCTION

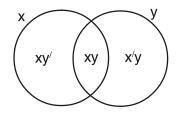

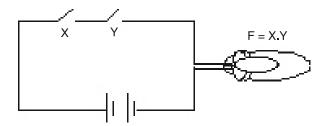

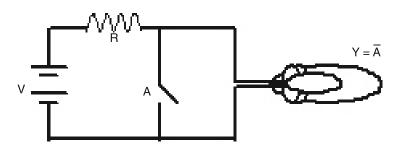

In this unit, you will be able to learn about the fundamentals of Boolean Algebra and logic operations. Three basic logic operations are AND, OR and NOT operations, where AND is logical multiplication, OR is logical addition and NOT is logical complementation. The logical AND operation between two variables X and Y is written as "X•Y". The result of X•Y is logical 0 for all cases except when both X and Y are logical 1. The logical OR operation is written as "X+Y", and produces a logical 1, when X or Y or both are logical 1. The logical NOT operation changes logical 1 to logical 0 and vice versa.

You will also learn the basic theorems and postulates of Boolean algebra, the principles of Duality, De Morgains theorem. Finally, you will learn about *sum of product* and *product of sums* simplification of Boolean functions using K-map.

## 2.3 BOOLEAN OPERATORS

Boolean algebra may be defined with the help of three sets of components viz,

- i) a set of elements,

- ii) a set of operators and

- a number of unproved axioms or postulates. A set of elements is any collection of objects having a common property.

A set of operators here is the binary operators, which are the rules that assigns to each pair of elements of the set a unique element from the set. The axioms or postulates form the basic assumptions from which it is possible to deduce the rules, theorems and properties of Boolean algebra. A variable in Boolean algebra can take only two vales, 1 (TRUE) or 0 (FALSE). i.e. TRUE is represented by 1 and FALSE is represented by 0. Boolean algebra is used for designing and analysing digital circuits. There are three basic operations in Boolean algebra and these operations are done with the help of three operators, viz. AND, OR and NOT. (These are also called basic logic operation).

**AND operation :** Boolean AND operator for two variables A and B can be represented as:

A and B or A.B or AB

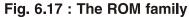

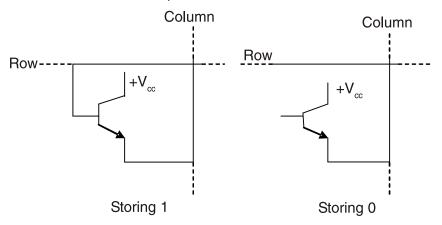

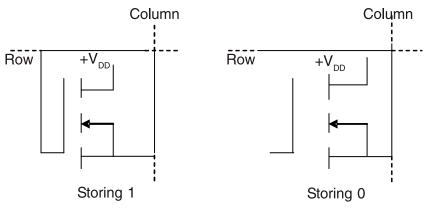

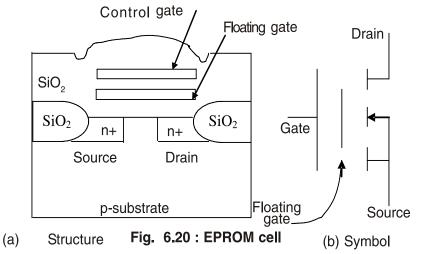

It results 1 or TRUE if both the operands A and B are 1 (TRUE), otherwise the result of 0 (FALSE).